PXIe-148X Getting Started Example - Basic Generation Tutorial

This tutorial teaches you the steps needed to configure a generation using a PXIe-148X module and familiarize you with the basic functionality provided by the Generation Getting Started Example and Create CSI-2 Packet TDMS Files VI.

Table of contents

- Prerequisites

- Initial Hardware Setup

- Initial Software Setup

- Create TDMS Files for Generation

- Performing a Simple Generation

- Performing a Simple Generation with GPIO Logging

- Related Documents

Prerequisites

Review and complete all setup from the appropriate getting started guide:

- PXIe-1486 Getting Started Guide

- PXIe-1487 Getting Started Guide

- PXIe-1488 Getting Started Guide

- PXIe-1489 Getting Started Guide

Basic knowledge of LabVIEW and LabVIEW FPGA concepts.

A supported interface module on a PXI system running a compatible Windows version.

| Interface Modules |

|---|

| PXIe-1486 (8 Out - 953 Serializer) |

| PXIe-1486 (4 In 4 Out - 953/954 SerDes) |

| PXIe-1487 (8 Out - 9295A Serializer) |

| PXIe-1487 (4 In 4 Out - 9295A/9296A SerDes) |

| PXIe-1488 (8 Out - 971 Serializer) |

| PXIe-1488 (4 In 4 Out - 971/9702 SerDes) |

| PXIe-1489 (4 Out - 96793 Serializer) |

| PXIe-1489 (2 In 2 Out - 96793/96792A SerDes) |

Initial Hardware Setup

Complete installation of hardware as described in the Getting Started Guide for your interface module. No physical connections to other modules or devices are required to complete this tutorial.

Initial Software Setup

Use the NI Example Finder to create a default project for your interface module.

- Complete installation of software specified in the Getting Started Guide for your interface module.

-

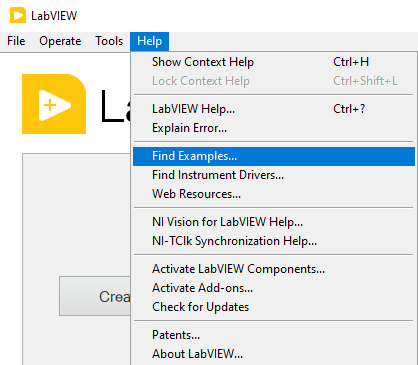

Open LabVIEW and click Help » Find Examples…

-

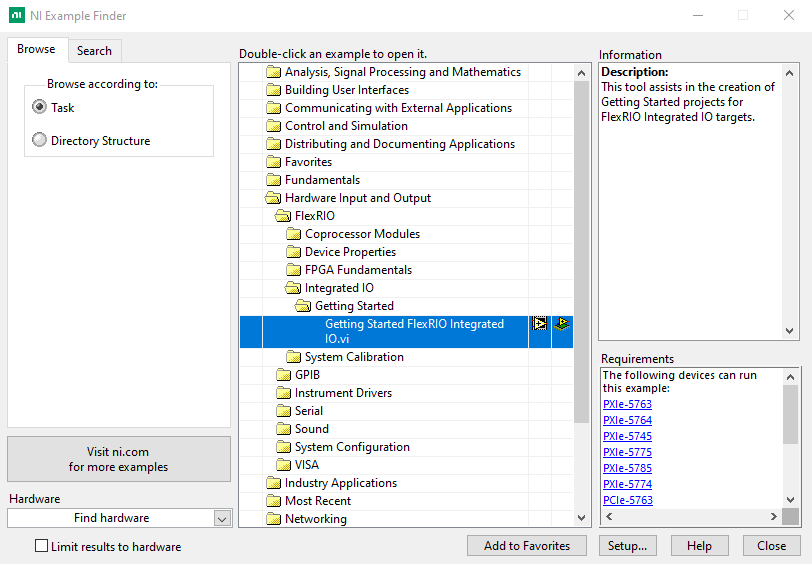

In the NI Example Finder dialog, double-click Hardware Input and Output » FlexRIO » Integrated IO » Getting Started » Getting Started FlexRIO Integrated IO.vi

-

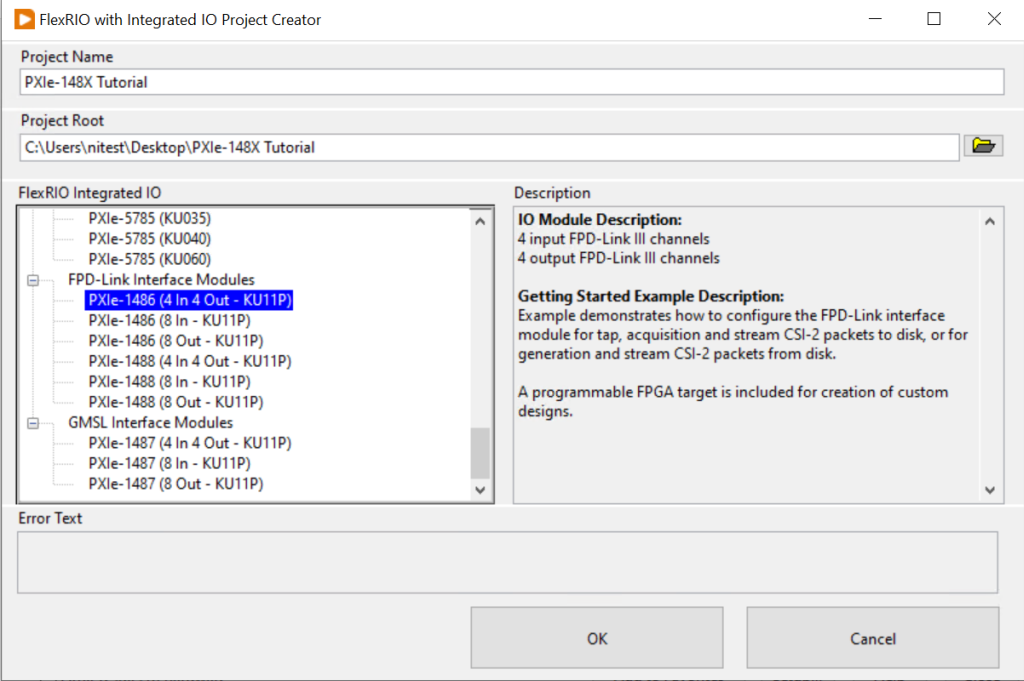

In the FlexRIO with Integrated IO Project Creator dialog, set the Project Name to PXIe-148X Tutorial, make the FlexRIO Integrated IO selection for the desired PXIe-148X interface module, and click OK.

Create TDMS Files for Generation

Create a TDMS file to house the image data you will generate during the tutorial.

Note: For the purposes of this tutorial, all input control values not specified should be left with their default values.

-

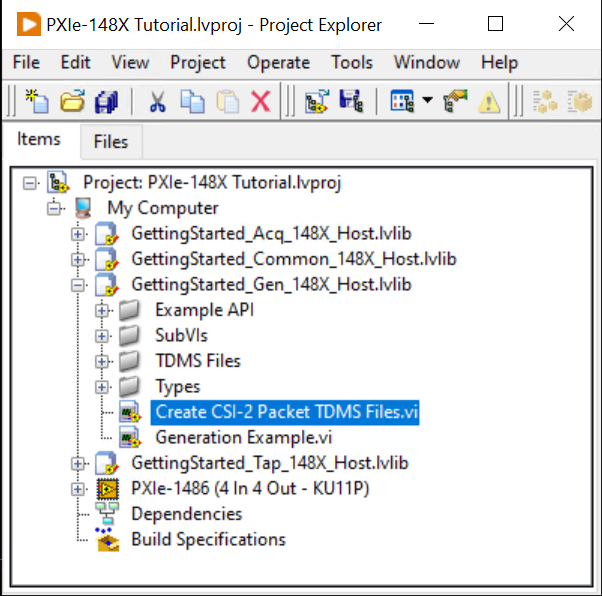

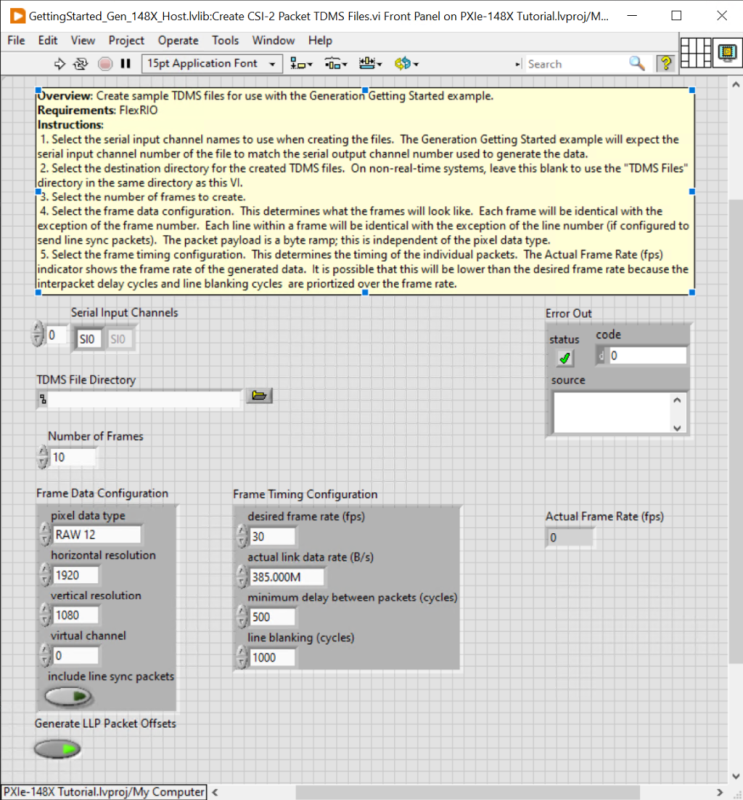

Double-click the Create CSI-2 Packet TDMS Files VI in the LabVIEW project.

The opened front panel of the Create CSI-2 Packet TDMS Files VI utility is similar to the figure below.

-

Review the instructions on the VI front panel; for this tutorial, the default settings are used to generate a TDMS file for channel SO0 containing 10 frames at 1920 × 1080 and 30 fps.

Note: During the first run of the VI, the TDMS File Directory control automatically populates with a value pointing to a subfolder ("TDMS Files"). This subfolder is automatically created within the project folder to store any generated TDMS files.

-

Run the VI to generate the TDMS file.

-

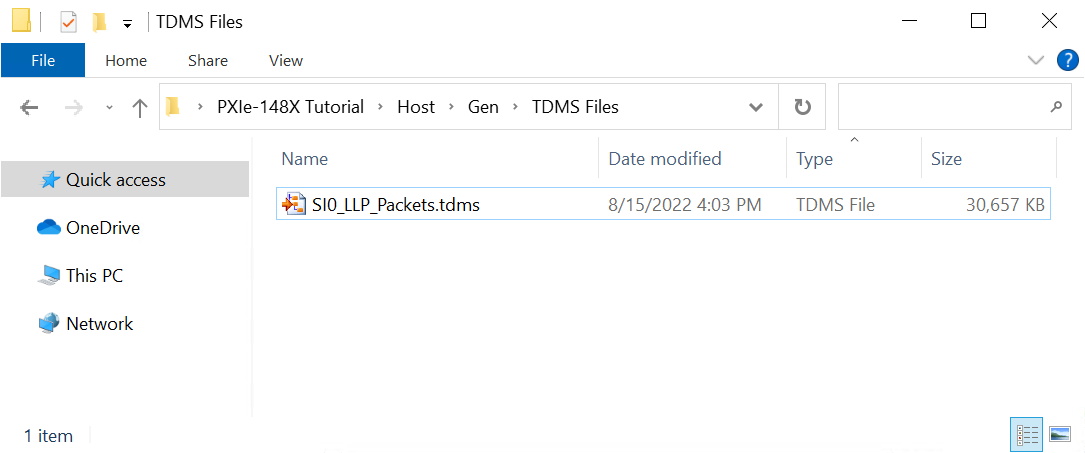

Open Windows Explorer and navigate to

<yourprojectdir>\Host\Gen\TDMS Files.The newly created TDMS file has the prefix “SI0_” to indicate it is associated with the first channel ‘SO0’. Although the ‘SI’ prefix suggests ‘serial input’, when used with the Generation GSE, the TDMS file actually associates with serial output channel ‘SO0’.

The newly created TDMS file is used in the next part of the tutorial to perform a simple generation.

Performing a Simple Generation

Complete this part of the tutorial to generate images, which will be stored to the TDMS file you created.

Note: For the purposes of this tutorial, all input control values not specified should be left with their default values.

-

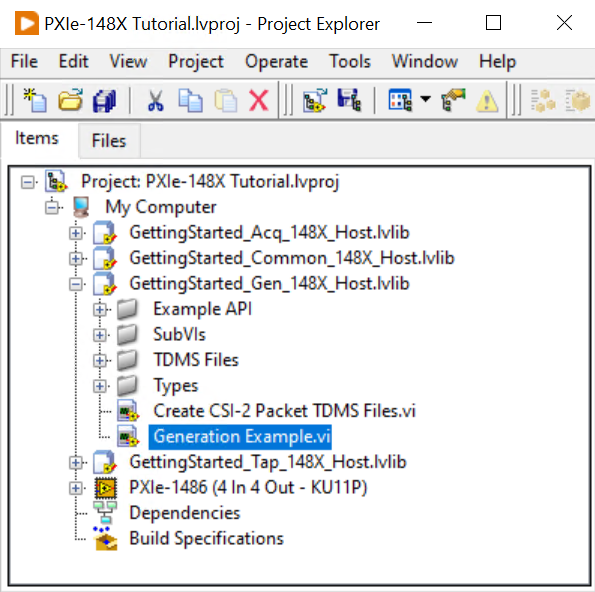

Double-click the Generation Example VI in the LabVIEW project.

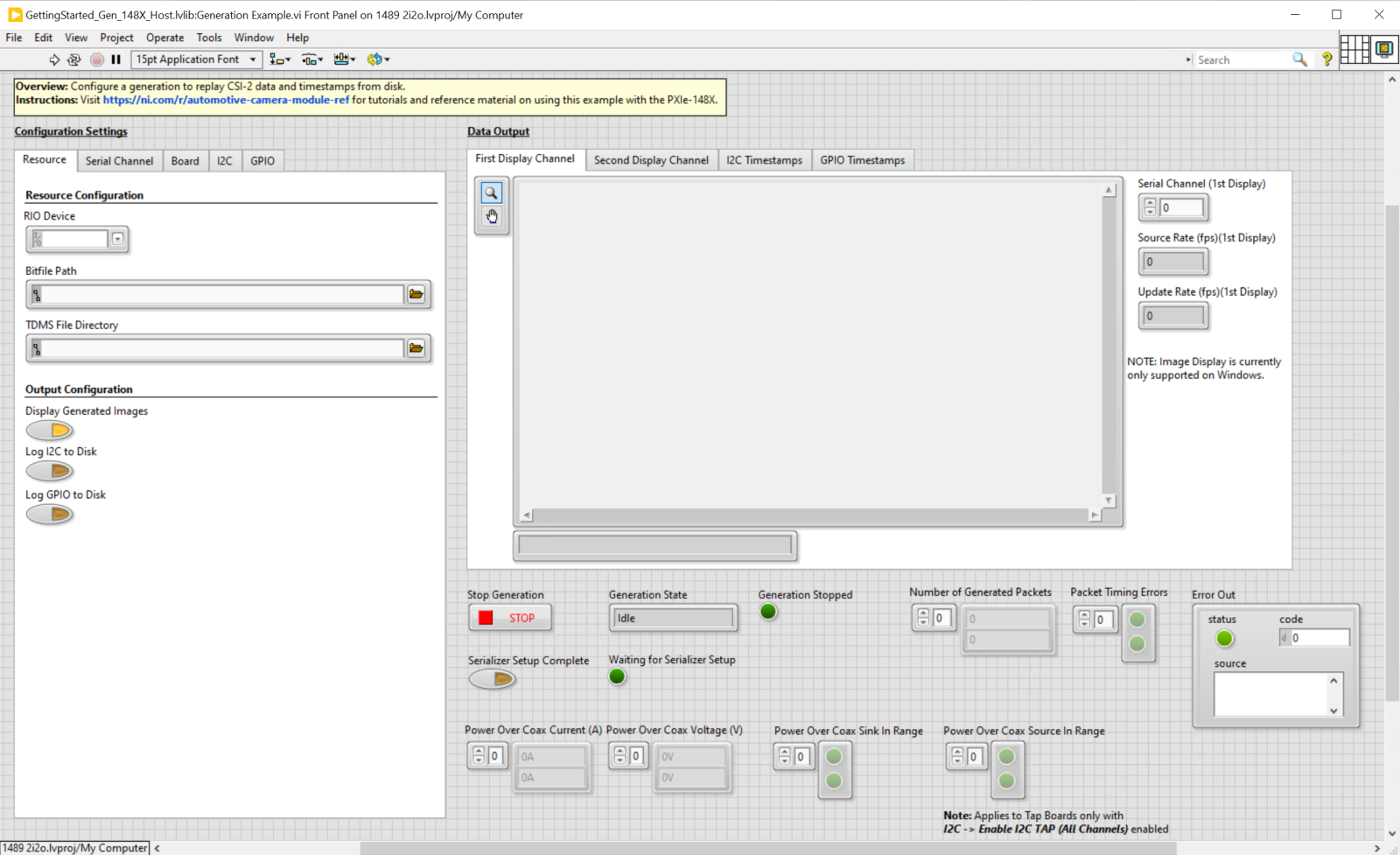

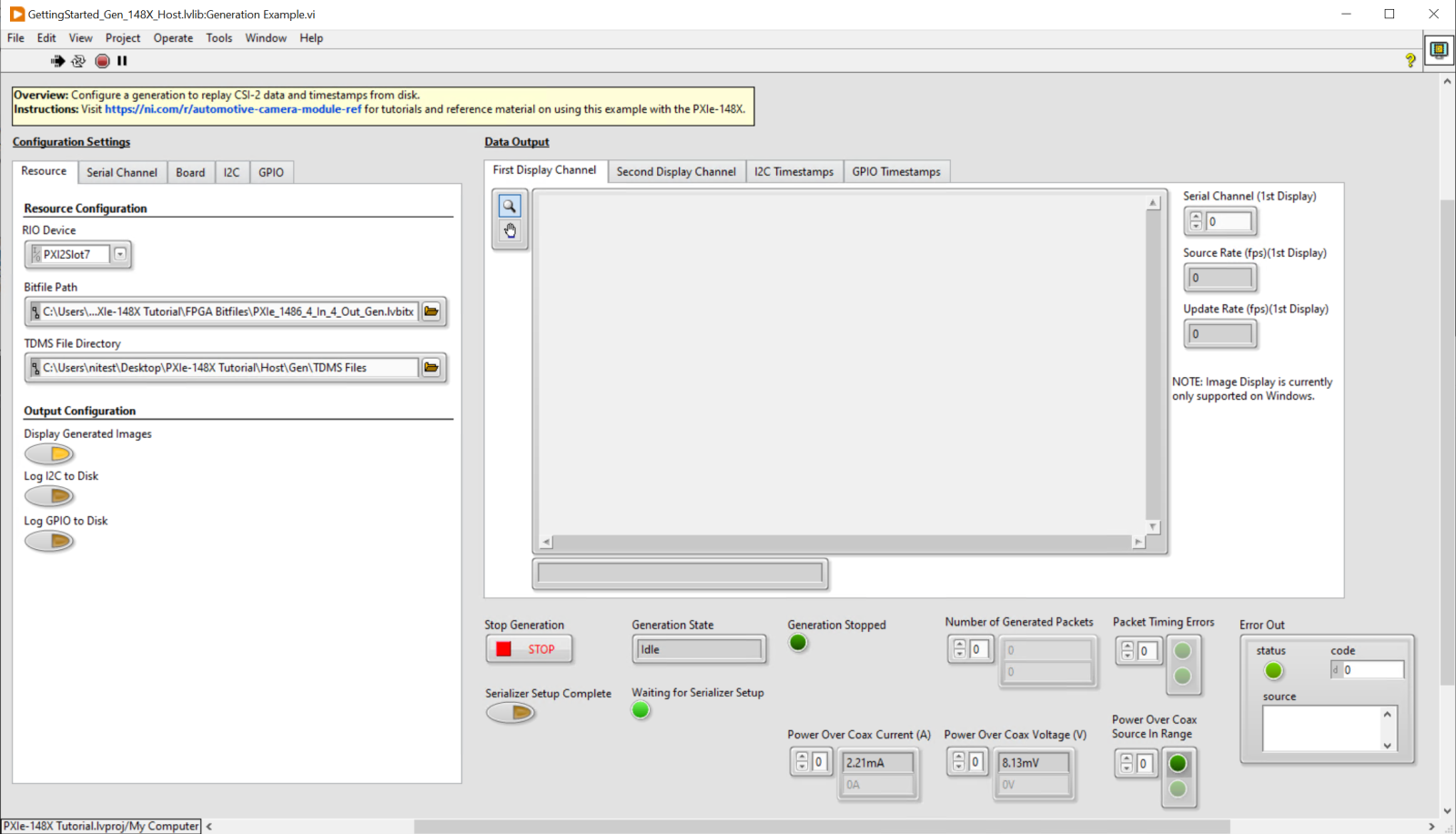

The opened front panel of the Generation Getting Started Example is similar to the figure below.

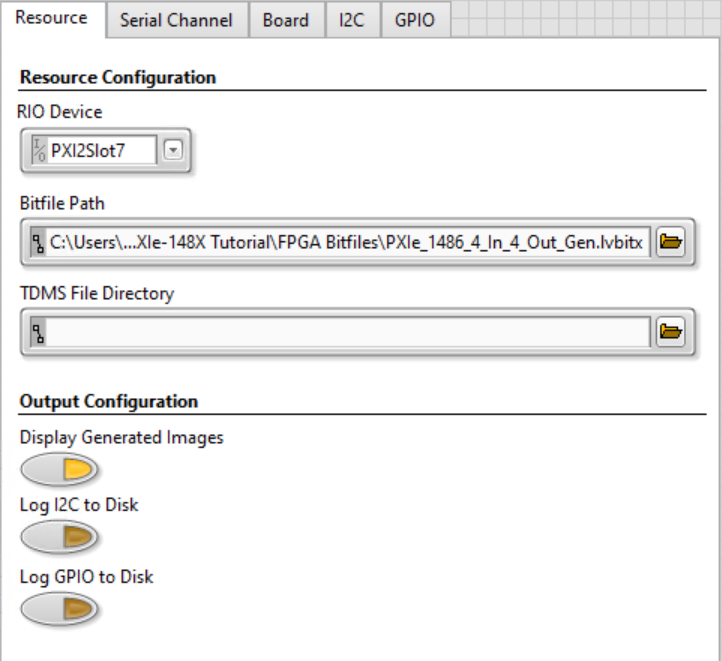

- Select the Resource tab and make the following modifications.

- Select the RIO Device from the dropdown menu that corresponds to your interface module.

- Set the Bitfile Path to the bitfile that corresponds to your interface module. The default shipping bitfile is in the

FPGA Bitfilessubfolder located in the project folder (created at the Project Root location specified in Project Creator):

Interface Module Bitfile PXIe-1486 (8 Out) FPGA Bitfiles\PXIe_1486_8_Out.lvbitx PXIe-1486 (4 In 4 Out) FPGA Bitfiles\PXIe_1486_4_In_4_Out_Gen.lvbitx PXIe-1487 (8 Out) FPGA Bitfiles\PXIe_1487_8_Out.lvbitx PXIe-1487 (4 In 4 Out) FPGA Bitfiles\PXIe_1487_4_In_4_Out_Gen.lvbitx PXIe-1488 (8 Out) FPGA Bitfiles\PXIe_1488_8_Out.lvbitx PXIe-1488 (4 In 4 Out) FPGA Bitfiles\PXIe_1488_4_In_4_Out_Gen.lvbitx PXIe-1489 (4 Out) FPGA Bitfiles\PXIe_1489_4_Out.lvbitx PXIe-1489 (2 In 2 Out) FPGA Bitfiles\PXIe_1489_2_In_2_Out_Gen.lvbitx The values on the Resource tab of Configuration Settings are now similar to the figure below.

Note: TDMS File Directory will be automatically populated when you run the VI.

-

Run the VI to perform a generation using the TDMS file created in the previous part of the tutorial.

The Generation GSE example loads the bitfile and then buffers available data from disk to the onboard DRAM of the interface module. After buffering, the Waiting for Serializer Setup indicator illuminates to indicate the module is ready for generation.

-

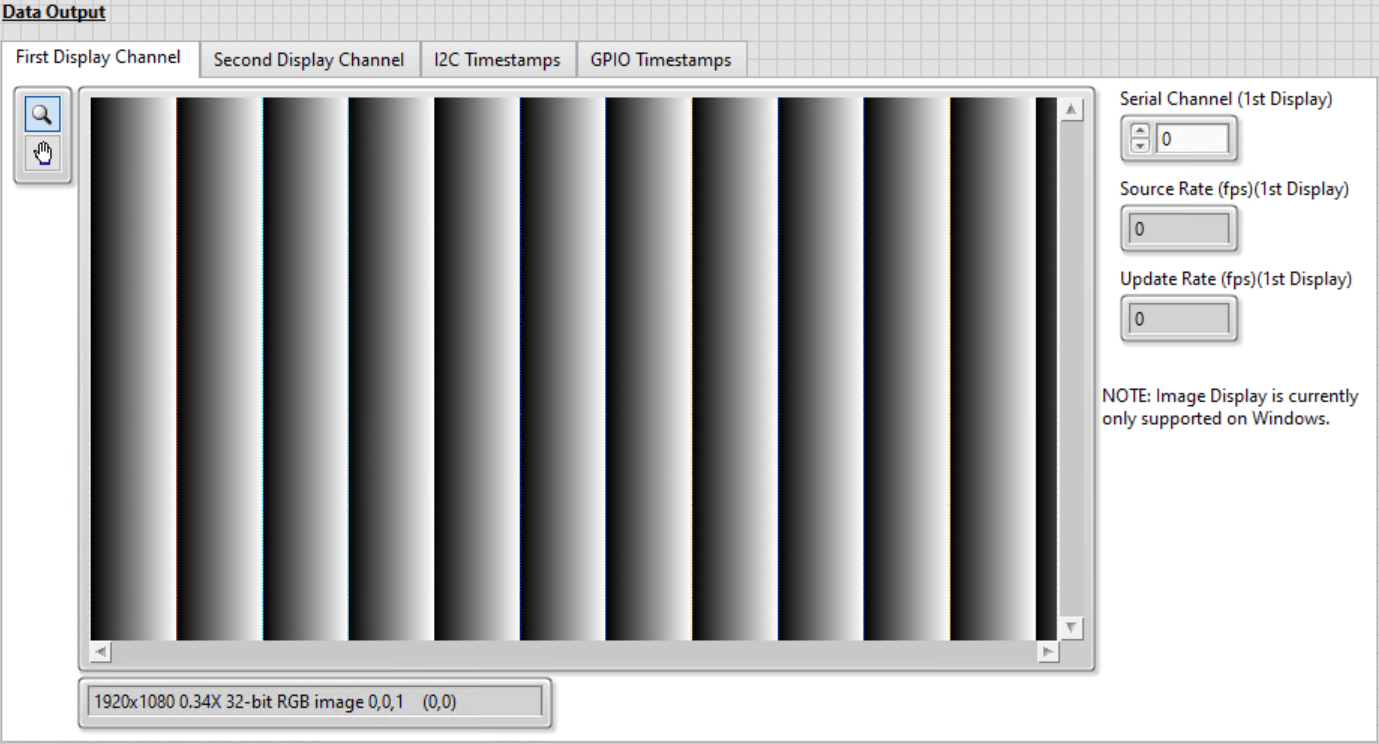

Click the Serializer Setup Complete control button to start generation. Generated images display automatically in the First Display Channel tab.

The VI stops automatically after all data from the TDMS file is generated.

Performing a Simple Generation with GPIO Logging

Note: This part of the tutorial assumes that all input parameters are still configured as specified in Performing a Simple Generation.

-

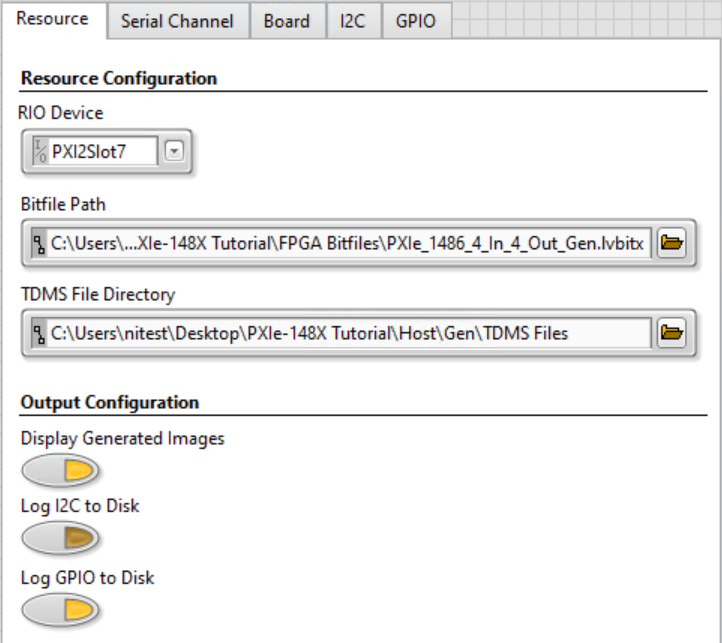

Select the Resource tab and make the following modifications.

- Enable Log GPIO to Disk.

Note: During the first run of the VI in Performing a Simple Generation, the TDMS File Directory control was automatically populated with a value pointing to a subfolder ("TDMS Files"). This subfolder was automatically created within the project folder to load any existing TDMS files.

The values on the Resource tab of Configuration Settings are now similar to the figure below.

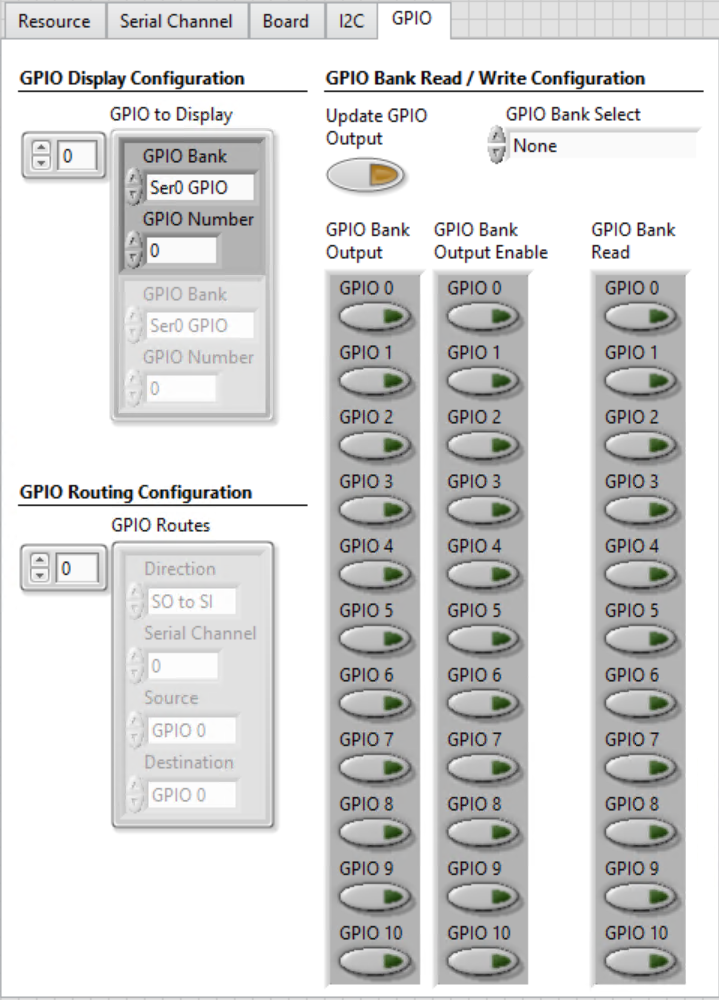

- Select the GPIO tab and make the following modifications.

- Add a GPIO line to the GPIO to Display array with the GPIO Bank value set to Ser0 GPIO and the GPIO Number set to 0. Setting these values enables display of GPIO traffic for the GPIO 0 line on the SO0 channel.

The values on the GPIO tab of Configuration Settings are now similar to the figure below.

-

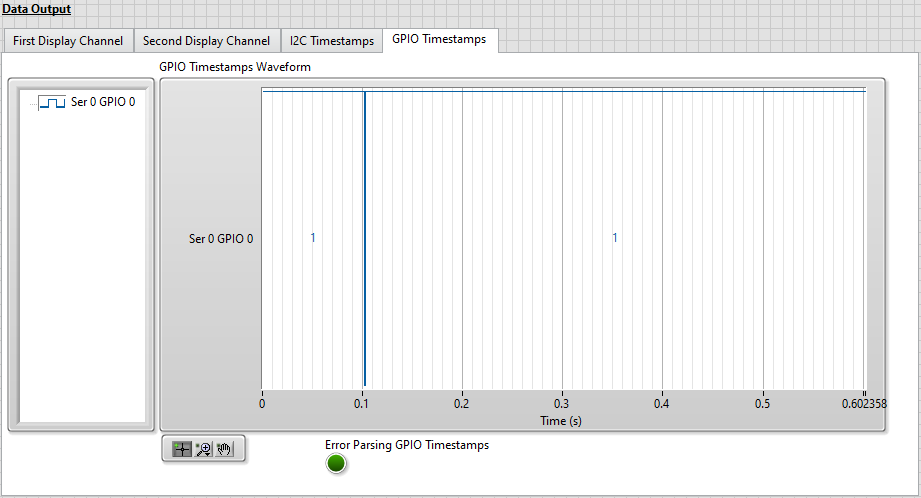

Run the VI, wait for the Waiting for Serializer Setup indicator to illuminate, and then click the Serializer Setup Complete control button to start the generation. Results are displayed on the various tabs in the Data Output indicator.

-

Click the GPIO Timestamps tab to view GPIO timestamp data for the GPIO lines included in the GPIO to Display array in Step 2.

Note: The module interface does not read/write (toggle) to GPIO by default. Any change shown in the figure above reflects GPIO level reset when the example VI is first run and may vary by module.